Home / المركز الإعلامي / مدونة / 2021 /

Customer & Partner Portal demo presented at ITAPA 2021 International Congress

· 3 minutes to read

Tachyum Emulation portal

During development of a new processor, close cooperation of architects, hardware, software, and verification teams is necessary. Architects are responsible for the design of the chip, its instruction set, fetching and evaluation process of each instruction, cooperation, and data exchange between CPU cores and between the entire CPU in a multi-socket configuration. Many more of their activities define overall properties, performance, and the processor’s ability to communicate with external peripherals.

Software teams

One of the software teams modifies opensource GCC and LLVM compilers to match the instruction set, memory and peripheral design to generate a highly efficient assembly code, fully utilizing the power of a freshly-designed processor.

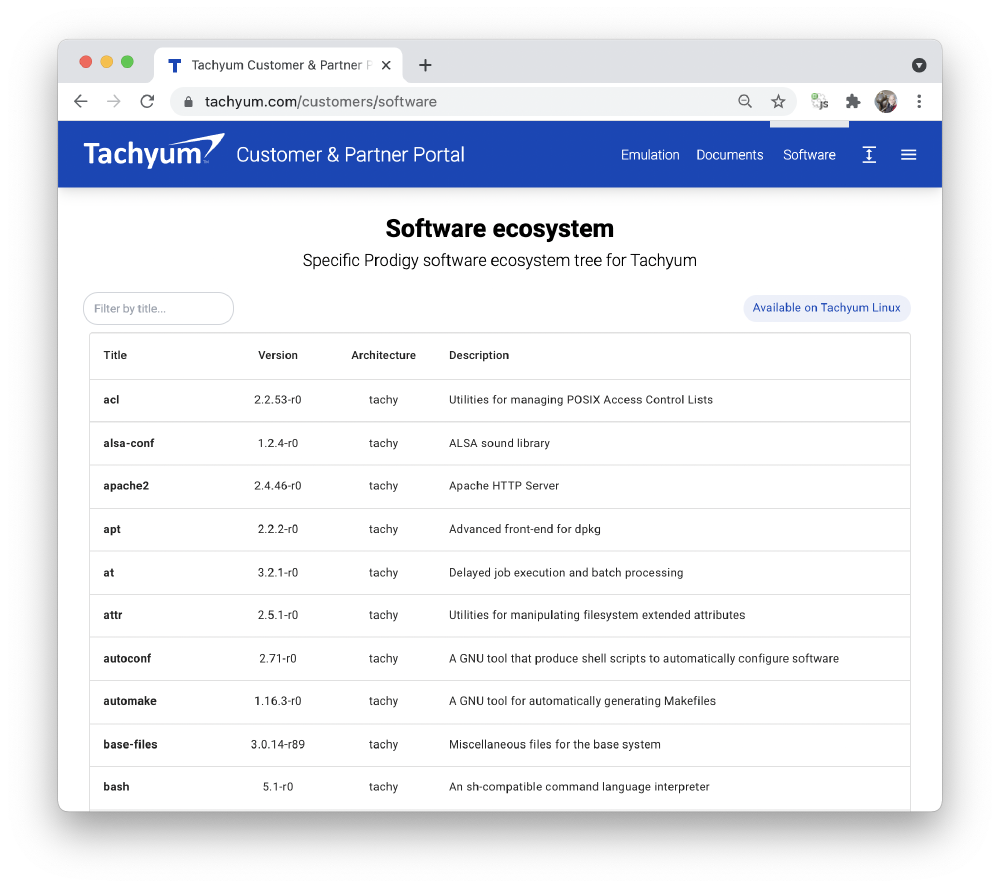

Building on their work, another software team modifies the operating systems to be able to seamlessly work on the brand new architecture. Besides operating systems, it is important to provide compatibility with widely used applications such as those which are intensively used in data centers: Database applications, webhosting and streaming tools, neural network training applications, tools for remote administration of servers, scientific packages…

You can find the list of currently supported software packages after logging into the Customer portal:

How can we check compatibility of such applications on our processor when it was not manufactured yet?

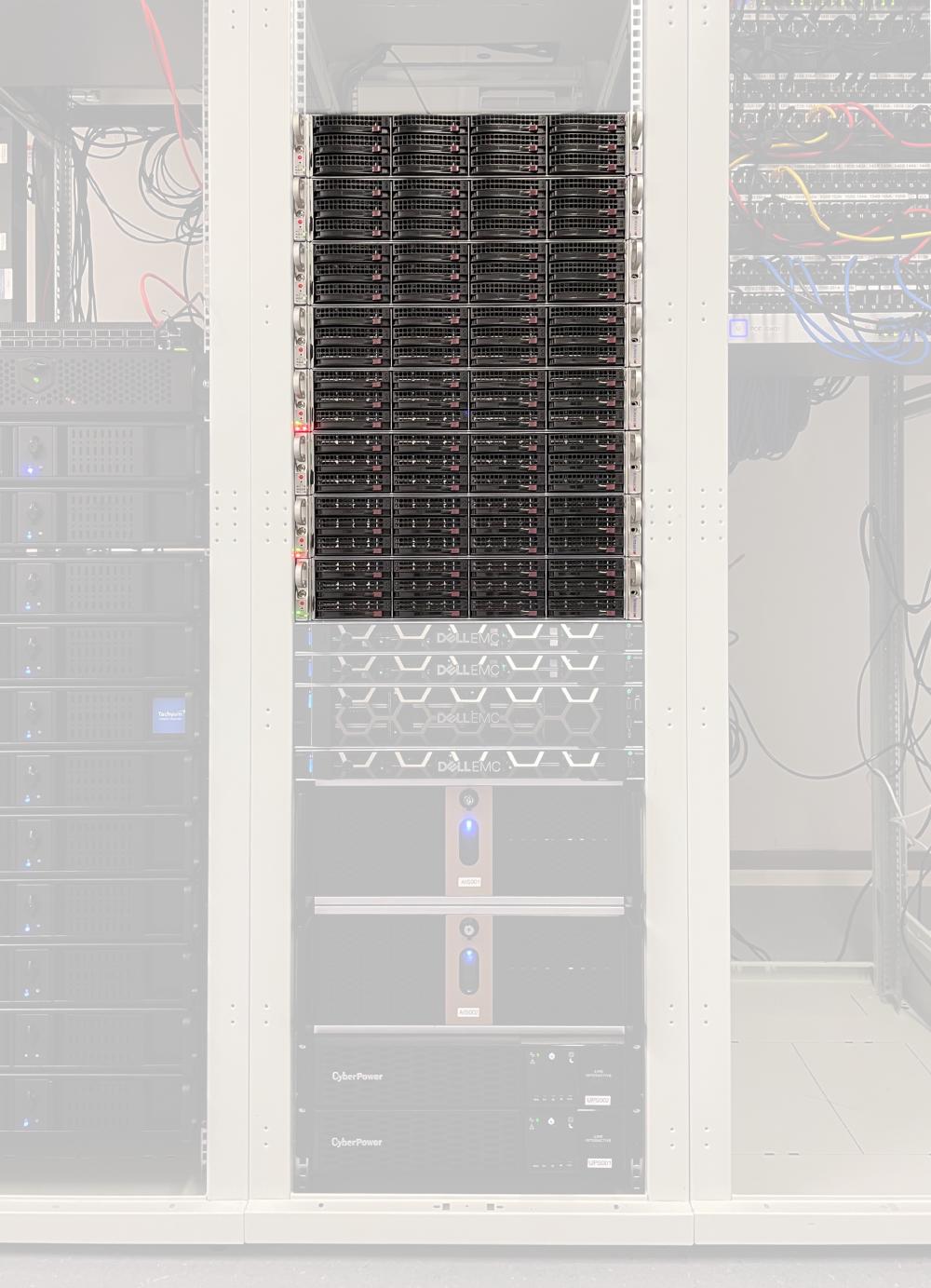

We are using a software emulator which precisely imitates the processes in our processor. This enables us to run and verify various software applications and operating systems even without having our hands on the Tachyum Prodigy processor. These emulators are running on our servers and our engineers are using them for verifying, testing and analyzing their performance.

Hardware teams

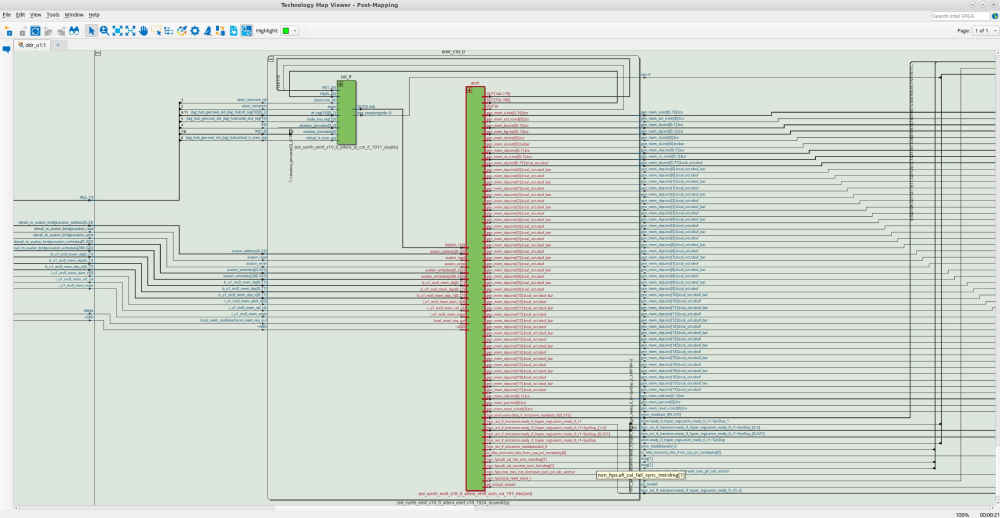

Hardware teams are working in parallel with software teams. They design the internal circuitry of the processor based on the architecture to match the required performance. This design is actually a huge schematic built of logic gates and function blocks which are used for interconnection with DDR5 memories or PCI express devices.

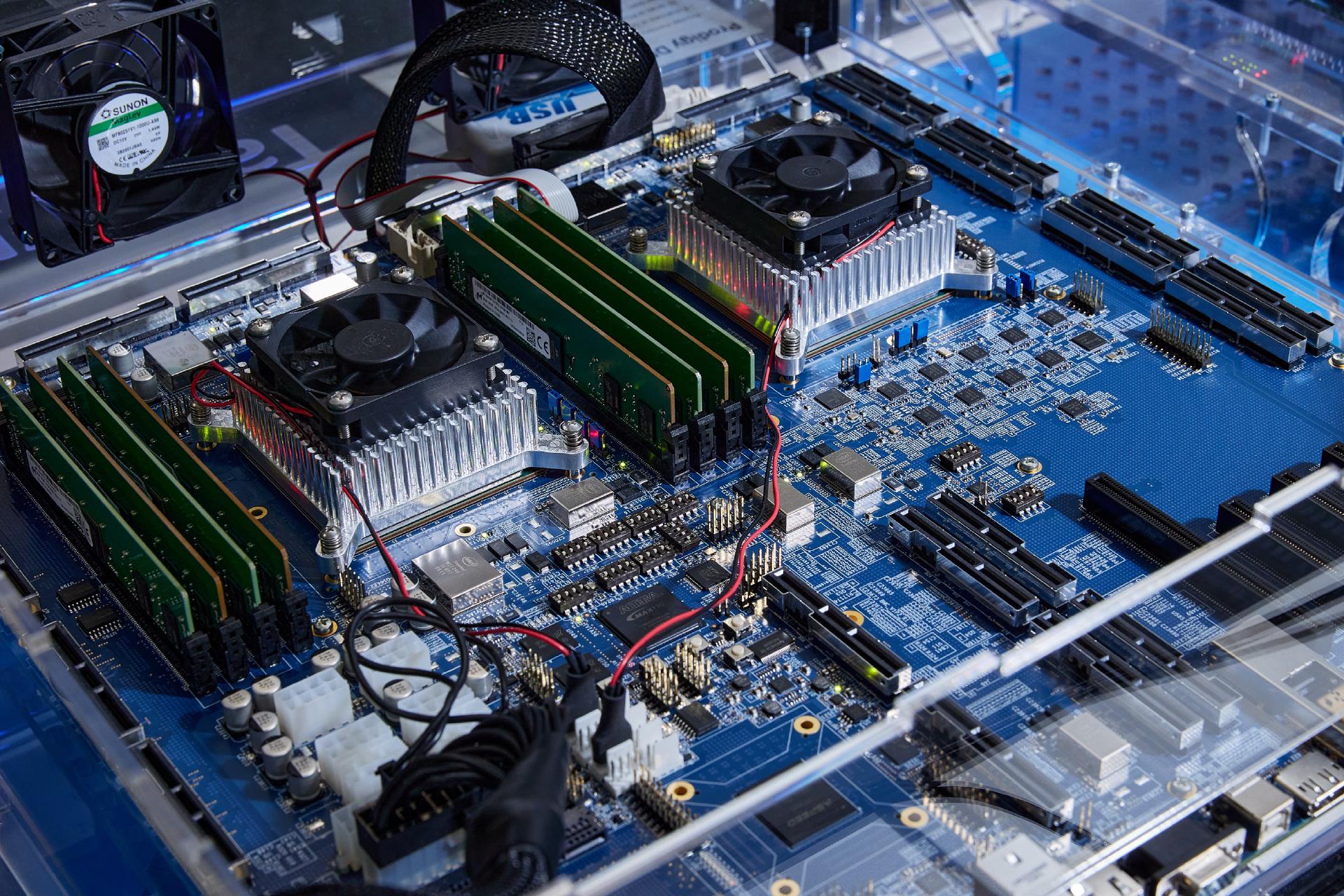

Such designs are subject to scrupulous checks done by the verification team. After this step, it is ready to be sent into the semiconductor fab for final design touches to match the production process. The same design can “run” on our FPGA prototype which uses one of the most advanced FPGA chips produced by Intel.

Our FPGA prototype is the final level in verification of our architecture and allows us to run complex algorithms and operating systems. Compared to software emulation, our FPGA based system uses real DDR RAM and real peripherals. This gives our engineers and partners opportunity to observe the system performance in real setup.

Emulation portal

The emulation portal grants our partners access to virtual machines running on the Tachyum Prodigy architecture as well as the FPGA prototype. That way they can test the compatibility of the tools they are using or ask our software team for assistance with porting these programs.

The following video depicts the process of logging in to the Emulation portal and using Linux 5.10.27 command line interface to:

- identify the system

- compile simple C application

- dump the assembly of this app

- clone and build apps from git repository

- run simple Java app

- list the attendees of ITAPA 2021 conference using Python

In this video following snippets of code were used:

- C/C++

#include <stdio.h>

int main()

{

printf("\n\n\t\tTachyum zdravi Itapu 2021\n\n\n");

return 0;

}

- Java

class ahoj {

public static void main(String args[])

{

System.out.println("\n\n\t\tAhoj Itapa 2021!\n\n"):

}

}

- Python

import re

import urllib.request

speakri = []

for i in range(9):

s = 'https://www.itapa.sk/9181-sk/spikri/?kongres=&page=%d' % i

f = urllib.request.urlopen(s)

html = f.read().decode('utf-8')

speakri += re.findall('<h3 class=\"title\">(.*)</h3>',html)

speakri.sort()

print(speakri)

Photogallery

See photos from ITAPA 2021 International Congress:

Contact our team at the email below for evaluation access to the Customer Portal